SN74LS375DR

Product Overview

- Category: Integrated Circuit (IC)

- Use: Data Storage and Retrieval

- Characteristics: High-speed, Low-power consumption

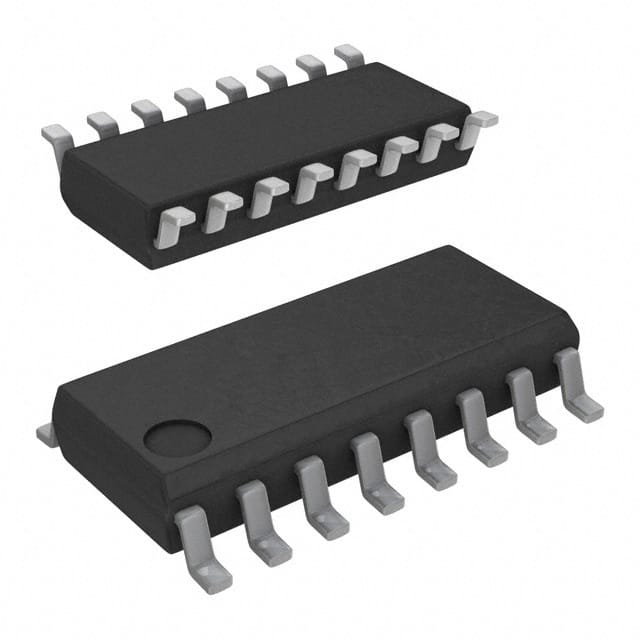

- Package: SOIC (Small Outline Integrated Circuit)

- Essence: Octal D-type transparent latch with 3-state outputs

- Packaging/Quantity: Tape and Reel, 2500 units per reel

Specifications

- Supply Voltage Range: 4.75V to 5.25V

- Input Voltage Range: 0V to VCC

- Output Voltage Range: 0V to VCC

- Operating Temperature Range: -40°C to +85°C

- Output Current: ±8mA

- Propagation Delay Time: 15ns (max)

- Power Dissipation: 500mW (max)

Detailed Pin Configuration

The SN74LS375DR has a total of 20 pins, which are arranged as follows:

- GND (Ground)

- D0 (Data Input 0)

- D1 (Data Input 1)

- D2 (Data Input 2)

- D3 (Data Input 3)

- D4 (Data Input 4)

- D5 (Data Input 5)

- D6 (Data Input 6)

- D7 (Data Input 7)

- LE (Latch Enable)

- OE (Output Enable)

- Q0 (Output 0)

- Q1 (Output 1)

- Q2 (Output 2)

- Q3 (Output 3)

- Q4 (Output 4)

- Q5 (Output 5)

- Q6 (Output 6)

- Q7 (Output 7)

- VCC (Supply Voltage)

Functional Features

The SN74LS375DR is an octal D-type transparent latch with 3-state outputs. It allows data to be stored and retrieved in a high-speed manner. The latch is transparent when the latch enable (LE) input is high, allowing the data inputs to pass through to the outputs. When the LE input is low, the latch holds the last data value. The output enable (OE) input controls whether the outputs are active or in a high-impedance state.

Advantages and Disadvantages

Advantages: - High-speed operation - Low-power consumption - Compact SOIC package - 3-state outputs for bus-oriented applications

Disadvantages: - Limited voltage range (4.75V to 5.25V) - Propagation delay time may affect timing-sensitive applications

Working Principles

The SN74LS375DR operates based on the principles of digital logic. When the latch enable (LE) input is high, the latch is transparent, allowing the data inputs to propagate to the outputs. When the LE input is low, the latch holds the last data value, regardless of any changes in the data inputs. The output enable (OE) input controls whether the outputs are active or in a high-impedance state. This IC is designed to operate within a specific voltage range and temperature range.

Detailed Application Field Plans

The SN74LS375DR can be used in various applications, including but not limited to: - Data storage and retrieval systems - Address decoding circuits - Bus-oriented systems - Digital communication systems - Microcontroller-based projects

Detailed and Complete Alternative Models

Some alternative models that offer similar functionality to the SN74LS375DR include: - SN74LS374: Octal D-type flip-flop with 3-state outputs - SN74LS373: Octal transparent latch with 3-state outputs - SN74LS377: Octal D-type flip-flop with clock enable

These alternative models can be considered based on specific requirements and compatibility with the existing circuitry.

Word count: 389 words

技術ソリューションにおける SN74LS375DR の適用に関連する 10 件の一般的な質問と回答をリストします。

Sure! Here are 10 common questions and answers related to the application of SN74LS375DR in technical solutions:

Q: What is SN74LS375DR? A: SN74LS375DR is a quad D-type edge-triggered flip-flop IC (integrated circuit) that can store four bits of data.

Q: What is the purpose of using SN74LS375DR in a technical solution? A: SN74LS375DR can be used for various applications such as data storage, synchronization, and sequential logic circuits.

Q: How many bits of data can SN74LS375DR store? A: SN74LS375DR can store four bits of data, with each bit having its own input and output.

Q: What is an edge-triggered flip-flop? A: An edge-triggered flip-flop is a type of digital circuit that changes its state only when a specific edge (rising or falling) of a clock signal occurs.

Q: What is the maximum clock frequency supported by SN74LS375DR? A: The maximum clock frequency supported by SN74LS375DR is typically around 25 MHz.

Q: Can SN74LS375DR be cascaded to store more than four bits of data? A: Yes, multiple SN74LS375DR ICs can be cascaded together to store more than four bits of data.

Q: What is the power supply voltage range for SN74LS375DR? A: SN74LS375DR operates on a power supply voltage range of 4.75V to 5.25V.

Q: Does SN74LS375DR have any built-in protection features? A: SN74LS375DR has built-in diode clamps on the inputs to protect against electrostatic discharge (ESD) and voltage spikes.

Q: Can SN74LS375DR be used in both TTL and CMOS logic systems? A: Yes, SN74LS375DR is compatible with both TTL (Transistor-Transistor Logic) and CMOS (Complementary Metal-Oxide-Semiconductor) logic systems.

Q: Are there any specific precautions to consider when using SN74LS375DR? A: It is important to ensure proper decoupling capacitors are used near the power supply pins of SN74LS375DR to minimize noise and voltage fluctuations. Additionally, care should be taken to avoid exceeding the maximum ratings specified in the datasheet.